Unit -> 1 Diode Circuits

Subject -> Analog Circuits

Faculty -> Dr Nidhi chauhan

Paper code -> BT 402

Lecture 5 -> Fet biasing

$$V_{GS2} = 5 - 0 = 5 \text{ V}$$

$V_{GS1} = 5 \text{ V} > V_T$  (its VT is negative), draws only leakage current, offers high resistance (R<sub>2</sub>)

is conducting, ON; offers very low resistance  $(R_1)$ . The circuit equivalent in this state is drawn in ig. 16.20(b).

Output

$$V_o \approx 0 \Rightarrow 0$$

-state

It can be seen from the circuits of Fig. 16.20(b) that

$$V_o = \frac{R_1}{R_1 + R_2} V_{SS} \approx 0 \text{ V}$$

2. Input

$$V_i = 0 \text{ V} \Rightarrow 0\text{-state}$$

$V_{GS2} = -5 \text{ V}, T_2 \text{ conducting (low resistance)}$

$V_{GS1} = 0 \text{ V}$ ;  $T_1$  nonconducting (high resistance)

Output

$$V_o \approx 5 \text{ V} \Rightarrow 1\text{-state}$$

We thus see that the circuit acts as an inverter; 1-state input produces 0-state output and 0-state input produces 1-state output.

It is observed in this circuit that only one transistor is turned on in any of the output states. As the ransistors are series connected, no current is drawn from the battery source in either of the two state Current is drawn from the battery only during state transition (either way). CMOS circuits, therefore, drawn extremely low power from the battery source and so their energy consumption is very small. This is t major attraction why CMOS is used in digital applications.

### FET BIASING 16.6

We shall consider only voltage-divider biasing as this is most commonly adopted. By examining the drain characteristics of the device, a Q-point is selected in the middle of the saturation region, which fixes  $V_{GSQ}$  and  $I_{DQ}$ . The biasing circuit resistors are to be selected for the device under de conditions to operate at the Q-point.

#### Voltage Divider Biasing 16.6.1

The circuit is drawn in Fig. 16.21. It is the same for any FET. As per voltage divider

$$V_G = \left(\frac{R_2}{R_1 + R_2}\right) V_{DD} \tag{16.8}$$

Then

$$V_{\alpha\alpha} = V_G - I_D R_S, I_S = I_D$$

$$V_{GS} = V_G - I_D R_S, I_S = I_D$$

$$I_D R_S \text{ provides stabilising negative voltage feedback.}$$

VDD

Fig. 16.21

(16.9)

Device transfer characteristic,

$I_D = f(V_{GS})|_{\text{Device Parameters}}; \text{ nonlinear}$

(16,10)

(16.11)

$I_D = f(V_{GS})|_{\text{Device Parameters}}$  and simultaneous solution of Eqs (16.8) and (16.9) yields KVL for DS load yields

$$V_{DSQ} = V_{DQ} - I_D(R_S + R_D)$$

,  $R_D$  has to be selected

Biasing analysis/design is then complete.

## Simultaneous Solution of Eqs. (16.9) and (16.10)

Equation (16.10) is the transfer characteristic of FET (nonlinear function of  $V_{GS}$ ). Equation (16.9) is a straight line, whose intersection with the transfer characteristic yields  $I_{DQ}$  and  $V_{GSQ}$ .

Substituting  $I_D$  from Eq. (16.9) in Eq. (16.10) leads to a quadratic equation in  $V_{GS}$  yielding two (ii) solutions from which the appropriate one is to be chosen.

## JFET

OI

Refer Fig. 16.21.

JFET:

$$I_{DSS} = 10 \text{ mA}, V_P = -6 \text{ V}$$

Circuit:

$$R_1 = 2.2 \text{ M}\Omega, R_2 = 280 \text{ k}\Omega, V_{DD} = 16 \text{ V}$$

$$R_D = 2 \text{ k}\Omega$$

,  $R_S = 1.5 \text{ k}\Omega$

To determine at Q-point

$$V_{GS}$$

,  $I_D$ ,  $V_{DS}$ ,  $V_{DG}$

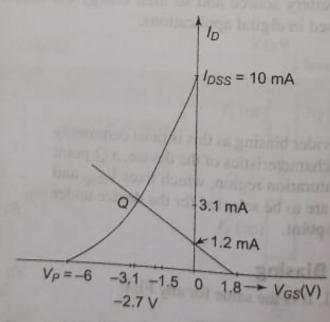

Plot the transfer characteristic (Fig. 16.22).

Fig. 16.22 Transfer characteristic

$$I_D = 10 \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$V_{GS} = -3 \text{ V}, \ \frac{V_{GS}}{V_P} = \frac{1}{2}, I_D = 2.5 \text{ mA}$

$$V_{GS} = 1.5 \text{ V}, \ \frac{V_{GS}}{V_P} = \frac{1}{4}, I_D = 5.265 \text{ mA}$$

plot Eq. (16.7).

$$V_G = \frac{280}{2.2 \times 10^3 + 280} \times 16 = 1.8 \,\mathrm{V}$$

$$V_{GS} = 1.8 - 1.5 I_D$$

$$I_D = 0$$

,  $V_{GS} = 1.8 \text{ V}$

$$V_{GS} = 0$$

,  $I_D = \frac{1.8}{1.5} = 1.2 \text{ mA}$

At intersection, Q-point

$$\Rightarrow V_{GS} = -2.7 \text{ V } I_D = 3.1 \text{ mA}$$

$V_{DS} = 16 - (2 + 1.5) \times 3.1 = 5.15 \text{ V}$

# Analytic Approach

From Eq. (16.13),

$$I_D = \frac{2.8 - V_{GS}}{1.5} = 1.2 - 0.67 V_{GS}$$

Substituting  $I_D$  in Eq. (16.13),

$$1.2 - 0.67 \ V_{GS} = 10 \left( 1 - \frac{V_{GS}}{-6} \right)^2$$

Let  $V_{GS} = x$

$$1.2 - 0.67x = 10\left(\frac{6+x}{6}\right)^2 = \frac{10}{36} (6+x)^2$$

$$4.32 - 2.41x = x^2 + 12x + 36$$

$$x^2 + 14.41x + 31.68$$

$$x = -2.7, -11.7$$

(rejected as more negative than  $V_P$ )

Then

$$V_{GS} = -2.7 \text{ V}$$

The same result as obtained by the graphical solution.

## **DMOSFET**

Refer Fig. 16.21.

**DMOSFET** parameters

$$I_{DSS} = 8 \text{ mA}, V_p = -4$$

Circuit data

$$V_{DD} = 16 \text{ V}$$

$R_1 = 100 \text{ M}\Omega, R_2 = 10 \text{ M}\Omega,$

$R_D = 1.6 \text{ k}\Omega, R_S = 700 \Omega$

To determine

(16.13)

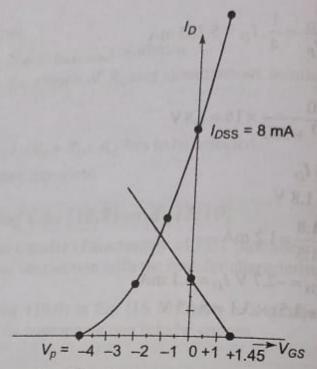

Fig. 16.23 Transfer characteristic

Plotting transfer characteristic (Fig. 16.23),

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$V_{GS} = -2 \text{ V}; I_D = 8 \left( 1 - \frac{1}{2} \right)^2 - 2 \text{ mA}$$

$$V_{GS} = -1 \text{ V}, I_D = 8 \left( 1 - \frac{1}{4} \right)^2 = 4.5 \text{ mA}$$

$$V_{GS} = +1 \text{ V}, I_D = 8 \left( 1 - \frac{1}{4} \right)^2 = 12.5 \text{ mA}$$

Plotting Eq. (16.8),

$$V_G = \frac{10}{100 + 10} \times 16 = 1.45 \text{ V}$$

$$V_{GS} = V_G - 0.7 I_D$$

$$I_D = 0 \qquad V_{GS} = V_G = 1.45 \text{ V}$$

$$V_{GS} = 0 \qquad I_D = \frac{1.45}{0.7} = 2.07 \text{ mA}$$

At intersection, Q-point

$$I_{DQ} = 3.8 \text{ mA}, V_{GSQ} = -1.2 \text{ V}$$

From Eq. (16.10),

$$V_{DSQ} = 16 - (1.6 + 0.7) \times 3.8 = 7.26 \text{ V}$$

EMOSFE I Refer Fig. 16.21. EMOSFET parameters

$$V_T = 4 \text{ V}, V_{GS(\text{on})} = 8 \text{ V}, I_{D(\text{on})} = 2.5 \text{ mA}$$

Biasing circuit

$$V_{DD} = 35 \text{ V}, R_1 = 20 \text{ M}\Omega, R_2 = 16 \text{ M}\Omega$$

$R_D = 2.5 \text{ k}\Omega, R_S = 0.75 \text{ k}\Omega$

To determine: At Q-point

$$I_{DQ}, V_{GSQ}, V_{DS}$$

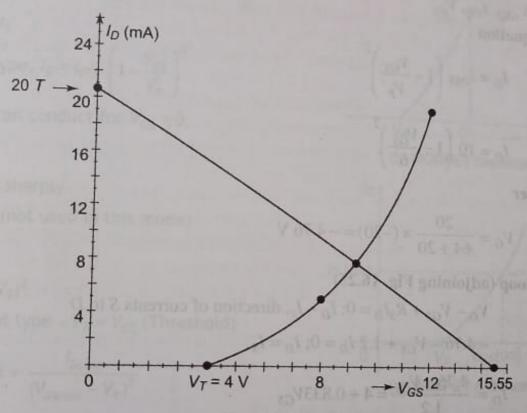

plot transfer characteristic (Fig. 16.24).

Fig. 16.24

$$k = \frac{2.5}{(8-4)^2} = 0.156 \text{ mA/V}^2$$

$$I_D = 0.156 (V_{DS} - 4)^2$$

$$V_{GS} = 8 \text{ V}, I_D = 0.156 \times 16 \text{ 2.5 mA}$$

$$V_{GS} = 12 \text{ V}, I_D = 0.156 \times 64 = 10 \text{ mA}$$

$$V_G = \frac{16}{20 + 16} \times 35 = 15.55 \text{ V}$$

$$V_{GS} = 15.55 - 0.75 I_D$$

$$V_{GS} = 0, I_D = 20.7 \text{ mA}$$

$$I_D = 0, V_{GS} = 15.55$$

At Q-point,

$$V_{GSQ} = 9.2 \text{ V}, I_{DQ} = 8.4 \text{ mA}$$

From Eq. (16.11),

$V_{DS} = 35 - (2.5 + 0.7) \times 8.4 = 8.12 \text{ V}$

-channel JFET

Channel JFET

Here Fig. 16.21 directions of  $I_D$  and  $I_S$  reverse,  $V_{DD}$  is negative, JFET parameters  $I_{DSS} \approx 10 \text{ mA}$ ,  $V_{p \approx 61}$

Biasing circuit

$$V_{DD} = -20 \text{ V}, R_1 = 64 \text{ k}\Omega, R_2 = 20 \text{ k}\Omega$$

$R_D = 2 \text{ k}\Omega. Rs = 1.2 \text{ k}\Omega$

To determine at Q-point

$$V_{GSQ}, I_{DQ}, V_{DS}$$

Shockley's equation

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$I_D = 10 \left( 1 - \frac{V_{GS}}{6} \right)^2$$

Voltage divider

$$V_G = \frac{20}{64 + 20} \times (-20) = -4.76 \text{ V}$$

KVL for GS loop (adjoining Fig. 16.25)

$$V_G - V_{GS} + R_S I_D = 0$$

;  $I_D - I_S$ ; direction of currents  $S$  to  $D$  -  $4.76 - V_{GS} + 1.2 I_D = 0$ ;  $I_D = I_S$

k= 2.5 = 0.156 mA/V

Am \$ 8 = 001, V 20 = 18 4 m A

0 = 8 V. In = 0.156 × 16 2.5 mA

or

$$I_D = \frac{4.76 + V_{GS}}{1.2} = 4 + 0.833V_{GS}$$

Let

$$V_{GS} = x$$

,

Substituting  $I_D$  in Eq (16.15),

$$4 + 0.833x = \frac{10}{36} (6 - x)^2$$

$$14.4 + 3x = 36 - 12x + x^2$$

$$x^2 - 15x + 21.6 = 0 \Rightarrow x = 1.6 \text{ V}, 13.476 \text{ V (rejected)}$$

Then,

$$V_{GSQ} = 1.6 \text{ V}$$

$$I_{DQ} = 10 \left( 1 - \frac{1.6}{8} \right)^2 = 5.38 \,\text{mA}$$

KVL DS loop,

$$-20 - (2 + 1.2) \times 5.38 - V_{DS} = 0$$

or

$$V_{DS} = -2.78 \text{ V}$$

Fig. 16.25

(16.15)